- Обновление Linux в устройстве на базе чипа Altera SoC FPGA и получение доступа к расшаренным ресурсам Windows-сервера

- Задачи

- Сборка ядра

- Сборка файловой системы

- Окончательная доводка

- DE0-Nano-SoC ещё один миникомпьютер для творчества

- FPGA+CPU или в данном случае Cyclone V SoC

- DE0-Nano-SoC

- Выводы

- Linux в устройстве на базе чипа Altera SoC FPGA: восстанавливаем утраченный функционал

- Небольшое лирическое отступление

- Итак приступим

- Проверка работоспособности

Обновление Linux в устройстве на базе чипа Altera SoC FPGA и получение доступа к расшаренным ресурсам Windows-сервера

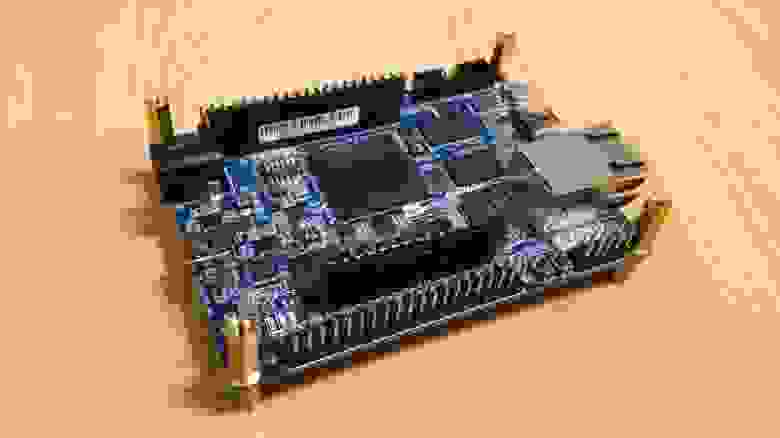

Недавно компания Terasic начала продажи весьма интересной платы DE0-Nano-SoC Kit. Интересна она тем, что за весьма скромную цену предлагается очень мощный и функционально-насыщенный комплект разработчика на основе чипа Altera Cyclone V SoC FPGA со встроенным двухъядерным процессором ARM Cortex-A9. Кроме того, производитель в комплекте с платой даёт ОС Linux, развёрнутую на карту памяти MicroSD.

Но получив эту плату в своё распоряжение, я довольно быстро наткнулся на несколько проблем, обусловленых тем, что Linux был скомпилирован из исходников Yocto Project. В основном все проблемы были связаны с отсутствием общедоступных репозиториев, из которых можно было бы добавить в систему недостающие компоненты. Например, для того, чтобы получить доступ с этого устройства через сеть к расшаренным ресурсам Windows-сервера, в ядре не хватало модуля поддержки файловой системы Cifs.

Поэтому прежде всего было решено обновить ядро, заменить Yocto на более привычный Debian Wheezy и доустановить всё, что необходимо для доступа к расшаренным ресурсам Windows-сервера.

Процесс сборки изучался мной и выполнялся следуя рекомендациям из этой статьи, за что её автору Des333 огромное спасибо!

Полная переделка в мои планы не входила, поэтому загрузчики на карточке было решено оставить родные — от образа Linux 3.13, идущего в комплекте с платой. Так что раздел с типом A2 было решено не трогать совсем.

Задачи

Сборка ядра

Так как основной моей рабочей средой по жизни является Windows, то все действия по сборке Linux выполнялись из-под ОС Linux Mint 17.2 Cinnamon, установленной на виртуальную машину.

1. Запускаем терминалку и входим в root-режим — чтобы не набирать каждый раз команду sudo:

При этом /root будет нашей домашней директорией — всё будем делать в ней.

2. Компилировать ядро будем с помощью кросс-компилятора, входящего в пакет Altera SoC Embedded Design Suite (EDS). Поэтому скачиваем и устанавливаем самый свежий пакет Altera SoC EDS. На данный момент времени Altera SoC EDS имеет версию 15.0. Скачать этот пакет можно прямо с сайта Альтеры.

Altera SoC EDS установится в директорию /root/altera/15.0.

3. Устанавливаем build-essential:

4. Установливаем libncurses:

5. Скачиваем исходники linux-socfpga из репозиториев Альтеры и распаковываем их в домашнюю директорию:

- Заходим в релизы linux-socfpga в репозиториях Альтеры

- Находим нужный релиз. Я выбрал версию 4.1 — так как это была самая свежая стабильная версия на данный момент времени

- Скачиваем архив с исходниками

- Распаковываем исходники в домашнюю директорию

В результате появляется директория /root/linux-socfpga-4.1 с исходниками ядра Linux версии 4.1.

Нужно брать не master и не tags а бренчи socfpga-*.

Например, socfpga-4.3

Именно туда накладывают патчи с нужной для SoC функциональностью.

Поэтому за исходниками нужно заходить сюда. Большое спасибо Des333 за подсказку!

6. Запускаем альтеровский скрипт, который запустит новый BASH и подправит в нём некоторые переменные окружения (например, PATH). Все действия по компиляции будем проводить не выходя из этого BASH:

7. Создаём несколько переменных окружения:

8. Создаём дефолтную конфигурацию для socfpga:

При этом будет создан конфигурационный файл .config, заточенный для компиляции под ARM.

9. Добавляем недостающие компоненты в конфигурацию ядра (или удаляем лишние):

Нам нужно добавить драйвер файловой системы CIFS — чтобы иметь возможность заходить на сетевые расшаренные ресурсы. Существует два способа добавления драйверов в систему — добавить прямо в ядро или добавить в виде внешних подключаемых модулей.

Итак, идём по пути File Systems -> Network File Systems, становимся на CIFS Support и нажимаем клавишу пробел — напротив строки CIFS Suport должна появиться буква M — значит будет использоваться подключаемый внешний модуль. Нужно будет позднее скомпилировать его отдельно и положить в директорию внешних модулей. Если же нажать клавишу пробел ещё раз, то буква M изменится на символ звёздочки — значит драйвер будет встроен прямо в ядро.

Примечание: в дальнейшем, при проверке работоспособности системы, выяснилось, что внешний модуль cifs крэшится при попытке копирования файла с расшаренного диска сервера Windows. Встроенный же в ядро драйвер cifs работал совершенно нормально. Хотя при использовании внешних модулей с другими версиями ядра (например, 3.19) подобных проблем не возникало. Причину происходящего мне так и не удалось выяснить.

Также нужно включить поддержку HighMem — иначе система не сможет использовать верхние 256 мегабайт ОЗУ. Для этого идём по пути Kernel Features -> High Memory Support и также нажимаем клавишу пробел.

Выходим из меню — нажимаем EXIT пока не выйдем. На вопрос — надо ли сохранять конфигурацию — отвечаем Yes.

10. Компилируем ядро:

В моём случае виртуальной машине было отдано только одно ядро. Процесс компиляции занял около 20 минут. Если же компилирование будет выполняться в машине с несколькими ядрами, то для скорости можно распараллелить процесс компиляции на несколько ядер. Для этого надо явно задать количество ядер через опцию -j. Например, для компиляции силами трёх ядер:

11. Компилируем dtb-файл, соответствующий нашему устройству. Если воспользоваться старым dtb-файлом, то или устройство повиснет при загрузке или будут страшные глюки при работе:

- Ищем все файлы, имеющие в названии cyclone5 и заканчивающиеся на dts:

В результате компиляции создалось два файла:

12. Если на этапе конфигурации был выбран вариант использования внешних модулей, то необходимо скомпилировать их.

Компилируем модуль CIFS:

и компилируем модули криптографии — они понадобятся при монтировании расшаренных ресурсов Windows:

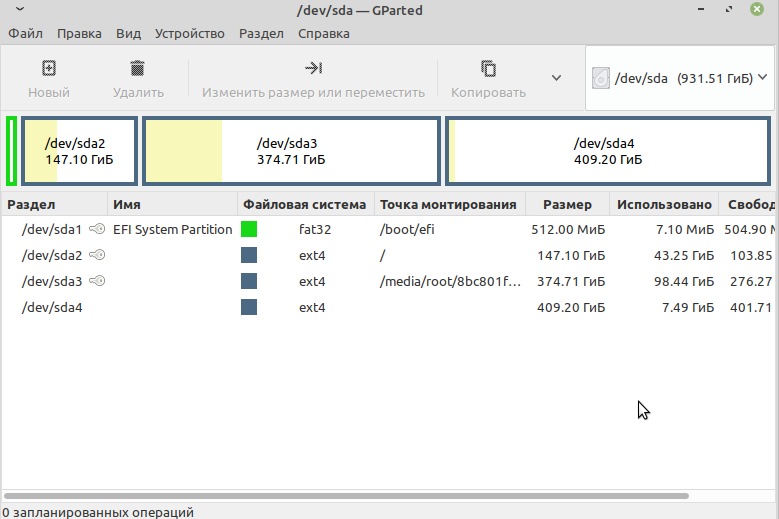

13. Копируем файлы ядра и dtb на карточку. Исходно карточка была нарезана так, что ядро и DTB-файл лежали на отдельном партишене FAT32. Вот на него эти файлы и записываем. Единственное замечание: DTB-файл нужно переименовать — чтобы он назывался также, как тот, который уже лежит на разделе FAT32 карточки:

- Подключаем карточку к виртуальной машине. Мне пришлось воспользоваться внешним кардридером, подключенным прямо к порту USB2 компьютера. Сделать то-же самое через встроенный в компьютер кардридер почему-то не удалось. Также не удалось подсоединить внешний кардридер к виртуальной машине, если подключать его через порт USB3.

- Произойдёт автомонтирование разделов карточки — нельзя размонтировать разделы через GUI, потому что в этом случае происходит полное отключение кардридера от виртуальной машины.

- Смотрим названия примонтированных разделов:

Увидим нечто в этом роде:

Раздел типа vfat (первая строка) — то, что нас интересует в данный момент.

Смотрим, что лежит на разделе vfat:

Видим нечто в этом роде:

Значит dtb-файл называется socfpga.dtb.

Копируем наши файлы на карточку:

Сборка файловой системы

Этот подраздел во многом повторяет то, что написано в этой статье, но тем не менее я привожу его полностью, чтобы в дальнейшем было проще пользоваться этим руководством.

Собирать будем Debian 7 Wheezy:

1. Устанавливаем пакеты, которые понадобятся для сборки файловой системы:

2. Создаем директорию и загружаем в неё все необходимые файлы:

3. Чтобы запускать приложения, собранные под ARM-архитектуру, будем использовать qemu static. Для этого скопируем файл в нашу директорию debian7:

4. Переходим в нашу новую файловую систему:

5. Если приглашение интерпретатора изменилось на «I have no name!@hostname:/#», значит всё прошло успешно.

Заканчиваем процесс сборки:

6. В /etc/inittab оставляем следующие строки:

7. Устанавливаем пароль для root-аккаунта:

8. Запаковываем новую файловую систему в архив:

9. Выходим из chroot:

10. Размонтируем и затем форматируем раздел ext3 на карточке (названия разделов смотрим в пункте 13 из сборки ядра):

11. Монтируем раздел ext3:

12. Распаковываем архив с файловой системой на карточку в раздел ext3:

13. Если при сборке ядра был выбран вариант использования внешних модулей, то необходимо записать на карточку внешние модули, скомпилированные на этапе 12 процесса сборки ядра:

14. Размонтируем разделы:

На этом всё — карточка готова, можно устанавливать её в устройство и загружаться.

Окончательная доводка

После загрузки устройства дотачиваем образ на месте:

1. Логинимся в Debian на устройстве, подключившись к нему через встроенный serial-порт.

2. Если при сборке ядра был выбран вариант использования внешних модулей, то необходимо сгенерить файлы с информацией о внешних модулях ядра:

3. Добавляем в список репозиториев репозиторий Debian 7 (я добавил немецкий сервер):

4. Подключаем устройство к Ethernet-сети. Получаем адрес по DHCP:

5. Поднимаем NTP, так как с неправильным временем не удастся примонтировать расшаренные ресурсы:

6. Устанавливаем наш часовой пояс:

7. Для проверки, что всё собралось нормально, монтируем серверную шару. Например, в моём случае я делал это так:

8. Устанавливаем SSH-сервер. Пользоваться serial-портом неудобно, так как при работе через него происходит заворот набираемых команд на начало строки после достижения колонки 80:

9. Назначаем статический адрес интерфейсу eth0 — чтобы в дальнейшем проще было подключаться к устройству по SSH. Для этого редактируем файл interfaces:

В моём случае он стал выглядеть вот так:

10. Редактируем файл resolv.conf — чтобы нормально работал DNS-клиент:

Добавляем в него строки:

11. Перезагружаем устройство.

12. Для проверки, что всё сделано правильно

Источник

DE0-Nano-SoC ещё один миникомпьютер для творчества

FPGA+CPU или в данном случае Cyclone V SoC

Один из вариантов решения проблемы может быть DevKit DE0-Nano-Soc. Данное решение построено на базе чипа Altera Cyclone V SE, а именно 5CSEMA4U23C6N. Который в свою очередь является комбинацией аппаратного ядра ARM Cortex A9 в данном случае двуядерным, и FPGA Cyclone V. Зачем может понадобиться такой тандем? А нужен он достаточно часто: FPGA хорошо подходит для быстрой обработки сигналов, обычные IO пины спокойно могут работать на сотнях мегагерц, а в моделях с аппаратными трансиверами и до шести гигагерц. А также для параллельной, конвейерной обработки поступающих сигналов. Однако описывать всё на языках вроде Verilog или VHDL достаточно сложно, медленно и неудобно. Поэтому достаточно часто была практика ставить в дизайн на FPGA реализацию процессора: специализированных NIOS II для Altera, MicroBlaze для Xilinx, варианты AVR ядер написанных энтузиазитстами и тому подобное. Из плюсов такого решения это простота, добавил в дизайн процессор и периферию и пиши себе программу на C/C++ для них, к минусам можно отнести то, что они во первых занимают ресурсы FPGA (логические ячейки, блоки памяти, PLL), во вторых достаточно медленны. Ну и в третьих несмотря на разнообразную периферию, она обычно достаточно проста, то есть поддержки DMA для UART в базовом наборе вы вряд ли найдёте, можно конечно написать своё, но это долго и достаточно сложно. С полными характеристиками чипа можно ознакомится здесь. Но рассмотрим детальней наш devkit.

DE0-Nano-SoC

Основной чип: Altera Cyclone V SE 5CSEMA4U23C6N

Часть аппаратного ядра(HPS):

- 1GB DDR3 SDRAM (32-bit data bus)

- 1 Gigabit Ethernet

- USB OTG Port, USB Micro-AB(работает как в режиме хоста так и девайса)

- Micro SD

- UART to USB, USB Mini-B connector

- Accelerometer (I2C interface + interrupt)

- Кнопки: cold reset, warm reset, user button

- Светодиод

- LTC разём расширения

Часть FPGA:

- EPCS128 для хранения конфигурации FPGA

- Две кнопки

- Четыре переключателя

- Восемь светодиодов

- Два 40пиновых разъёма(36 GPIO+2GND+5V Pin+3V Pin) стандарный для плат от Terasic.

- Разъём расширения совместимый с Arduino Uno R3

- Аналого цифровой преобразователь 8ми канальный

Выводы

Плата достаточно мощная, имеет гибкую конфигурацию, может быть использована в домашних разработках, если нужна высокая скорость или нестандартные интерфейсы, которые можно реализовать на FPGA стороне. Отлично подойдёт для повышения скила как в разработке для FPGA, так и в программировании ARM. Однако, для начального обучения FPGA я бы её не посоветовал из-за малого количества установленной периферии. Она всё же больше плата для использования, в каком либо устройстве, как готового блока управления. Ну и немного подводя итоги:

Плюсы:

- ARM Cortex A9

- FPGA часть на базе Cyclon V(на данный момент самый современный чип семейства Cyclone)

- Гибкая конфигурация: FPGA часть может использовать большую часть пинов HPS части, а в свою очередь HPS часть может направлять сигналы с периферии(UART/SPi/I2C/CAN) «внутрь» FPGA а не только на заданные ноги.

- 72 GPIO выведенных с FPGA части.

- 8 каналов ADC

- 1 Gb Ethernert

- USB OTG порт

Минусы:

- Цена: 99$ что достаточно дорого на фоне Raspberry Pi и её аналогов

- Сложность: придётся работать как с FPGA так и с ARM частью

- документация: документация на сам devkit очень подробна, а вот с документацией на сам чип местами всё достаточно плохо, если FPGA часть описана хорошо, то вот с HPS не так всё радужно, некоторые моменты описаны совсем не интуитивно и можно сказать поверхностно, хотя основные моменты всё же описаны хорошо.

- Сообщество: его можно сказать нет

Достаточно мощная и интересная плата, но как всегда за гибкость приходится платить сложностью в освоении. Если есть, какие либо вопросы по этой плате, задавайте в комментариях, постараюсь ответить.

Источник

Linux в устройстве на базе чипа Altera SoC FPGA: восстанавливаем утраченный функционал

Некоторое время назад ко мне в руки попал набор разработчика DE0-Nano-SoC, построенный на базе чипа Altera Cyclone V. Данный набор используется мной не с какой-то одной целью — с его помощью решаются разные задачи. Для каждой из этих задач создаётся схема для FPGA и пишется программа для HPS. Схема для FPGA создаётся в среде Quartus II и в процессе разработки загружается в FPGA через JTAG-интерфейс посредством USB-бластера. Когда же схема окончательно отлажена, она записывается на SD-карточку в виде файла прошивки. Затем, когда нужно использовать плату с той или иной целью, берётся нужная прошивка, загружается в FPGA командой вида

и затем запускается нужная программа.

Всё шло своим чередом, но однажды я обновил в плате ядро Linux — о чём рассказывал в этой статье. И вот спустя некоторое время обнаружилось, что из списка драйверов исчез FPGA-менеджер, позволявший загружать прошивку в FPGA подобным способом. Первой мыслью было то, что я забыл включить драйвер в конфигурацию при сборке ядра. Однако, к моему удивлению, скоро обнаружилось, что среди исходников ядра этого драйвера нет в принципе! Конечно, можно было бы грузить прошивку в FPGA другими способами, коих есть ещё как минимум три. Но этот способ был для меня наиболее оперативным и удобным, вот почему было принято решение восстановить утраченный функционал. Если Вам интересно, как это было сделано — добро пожаловать под кат.

Небольшое лирическое отступление

Для решения проблемы прежде всего нужно было найти исходные тексты FPGA-менеджера. Естественно, первым делом были обследованы репозитории Альтеры. И опять же я был удивлён тем, что этого драйвера в них не оказалось. Пришлось искать по всему гитхабу и в результате исходники были найдены в репозиториях Терасика. И тут опять образовались грабли: Терасик давно не публиковал ничего на гитхабе и самое свежее ядро было версии 3.12. Как следствие, взятые из этого репозитория исходники FPGA-менеджера отказывались компилироваться под новые ядра из-за того, что в них использовались некоторые «устаревшие» структуры, попросту ликвидированные из новых версий. Переделывать драйвер под новые реалии что-то меня никак не тянуло. Поэтому поиск был продолжен и в конце концов увенчался таки успехом — нашлись адаптированные исходники драйвера в репозитории некоего мистера из Канады с ником xaxaxa. За что ему низкий поклон.

Итак приступим

Подробности сборки ядра можно посмотреть в моей предыдущей статье — далее, чтобы не повторяться, я буду ссылаться на неё время от времени. Всё дальнейшее повествование будет построено на предположении, что весь процесс сборки ядра, описанный в той статье, уже выполнен и все исходники ядра лежат на прежнем месте в целости и сохранности.

1. Запускаем терминалку и входим в root-режим — чтобы не набирать каждый раз команду sudo:

При этом /root будет нашей домашней директорией — всё будем делать в ней.

2. Скачиваем исходники драйвера FPGA-менеджера отсюда и кладём в директорию /root/linux-socfpga-4.1/drivers/fpga/

Также забираем отсюда хидер fpga.h и записываем его в директорию /root/linux-socfpga-4.1/include/linux/

3. Редактируем файл /root/linux-socfpga-4.1/drivers/Kconfig — добавляем в него одну строку:

Куда конкретно её добавить — особого значения не имеет. Главное, чтобы она была не самой первой и не самой последней строкой файла. Я добавил её сразу после первой строки. Получилось вот так:

4. Редактируем файл /root/linux-socfpga-4.1/drivers/Makefile — добавляем в него одну строку:

Куда конкретно её добавить — опять же значения не имеет. Я добавил её сразу после начальных комментариев. Получилось вот так:

5. Запускаем альтеровский скрипт, который запустит новый BASH и подправит в нём некоторые переменные окружения (например, PATH). Все действия по компиляции будем проводить не выходя из этого BASH:

6. Создаём несколько переменных окружения:

7. Переходим в директорию с исходниками ядра и добавляем драйвер FPGA-менеджера в конфигурацию ядра:

При этом откроется псевдографическое окно с менюшками. Заходим в подменю Device Drivers. Здесь увидим, что на первом месте появилось новое подменю FPGA devices — заходим в него. Внутри будет драйвер FPGA Framework — добавляем его в ядро: нажимаем на нём пробел дважды — при этом напротив него появится символ звёздочки, говорящий о том, что данный драйвер будет встроен в ядро. Сразу после выполнения этих действий в списке появится ещё один драйвер Altera — включаем и его тоже: нажимаем на нём дважды пробел:

Так как мы сейчас не выполняли сброс конфигурации в исходное состояние командой make socfpga_defconfig, то остальные настройки должны остаться в прежнем состоянии — как мы их установили в процессе сборки ядра.

Выходим из меню — нажимаем Exit пока не выйдем. На вопрос — надо ли сохранять конфигурацию — отвечаем Yes.

8. Компилируем ядро:

Так как ядро компилировалось нами ранее, то теперь на его пересборку с новыми драйверами уйдёт совсем мало времени.

9. Добавляем в дерево устройств информацию о FPGA-менеджере.

Для этого добавляем в файл /root/linux-socfpga-4.1/arch/arm/boot/dts/socfpga.dtsi следующие строки:

Эти строки можно добавить в блок soc.

10. Конвертируем файл дерева устройств в бинарный формат:

11. Копируем ядро и .dtb-файл на карточку в раздел FAT32. Повторяться не буду: о том, как это сделать, подробно описано в подразделе 13 раздела Сборка ядра этой статьи.

На этом всё — процесс сборки ядра в комплекте с драйвером FPGA-менеджера завершён.

Проверка работоспособности

Поставим SD-карточку в плату, загрузимся и проверим работоспособность.

Для этого сначала посмотрим содержимое директории /dev — в ней должен появиться файл драйвера fpga0:

Ну и в завершение загрузим какую-нибудь прошивку в FPGA:

Источник